# Enhancement-Mode InAlN/AlN/GaN HEMTs With 10<sup>-12</sup> A/mm Leakage Current and 10<sup>12</sup> ON/OFF Current Ratio

Ronghua Wang, Paul Saunier, *Senior Member, IEEE*, Yong Tang, Tian Fang, Xiang Gao, Shiping Guo, *Member, IEEE*, Gregory Snider, *Senior Member, IEEE*, Patrick Fay, *Senior Member, IEEE*, Debdeep Jena, *Member, IEEE*, and Huili Xing, *Member, IEEE*

Abstract-Postprocessing annealing in forming gas at 400 °C performed on enhancement-mode lattice-matched was InAlN/AlN/GaN high-electron-mobility transistors fabricated by selective etch of InAlN under a Pt gate. After postprocessing annealing, the device reverse gate leakage current decreased from  $10^{-7}$  to  $10^{-12}$  A/mm at  $V_{\rm gs} = -1$  V and  $V_{\rm ds} = 6$  V, showing an ON/OFF current ratio of  $10^{12}$  that is the highest reported value for all GaN-based transistors. The gate diode breakdown voltage was observed to increase from  $\sim$ 9 to  $\sim$ 29 V; the transistor threshold voltage was also found to shift from 0.6 to 1.2 V. All these observations indicate that an electrically thinner and more insulating interlayer is most likely formed between the Pt gate and underlying channel after postprocessing annealing, which is ascribed to multiple possible mechanisms including increase in barrier height, reduction in interface states introduced during the gate recess process, formation of a thin oxide layer, etc.

*Index Terms*—Enhancement mode (E-mode), gate leakage current, InAlN, postprocessing annealing.

## I. INTRODUCTION

ATTICE-MATCHED InAlN/GaN high-electron-mobility transistors (HEMTs) have attracted a lot of attention recently due to the demonstrated high drain current density [1] and superior thermal stability [2] for power electronics, as well as high speed [3]. However, low gate leakage current is still a challenge for GaN-based transistors, since high gate leakage current causes extra noise in power amplifiers [4], additional loss at OFF state in power supplies [5], as well

Manuscript received October 15, 2010; revised November 12, 2010; accepted November 20, 2010. Date of publication January 6, 2011; date of current version February 23, 2011. This work was supported by the Defense Advanced Research Projects Agency (John Albrecht, the NEXT Program HR0011-10-C-0015). The review of this letter was arranged by Editor J. A. del Alamo. The views, opinions, and/or findings contained in this letter are those of the author/presenter and should not be interpreted as representing the official views or policies, either expressed or implied, of the Defense Advanced Research Projects Agency or the Department of Defense.

R. Wang, Y. Tang, T. Fang, G. Snider, P. Fay, D. Jena, and H. Xing are with the Department of Electrical Engineering, University of Notre Dame, Notre Dame, IN 46556 USA (e-mail: rwang@nd.edu; yongtang@ alumni.nd.edu; tfang@nd.edu; snider.7@nd.edu; pfay@nd.edu; djena@nd.edu; hxing@nd.edu).

P. Saunier is with Triquint Semiconductor, Inc., Richardson, TX 75080 USA (e-mail: paul.saunier@tqs.com).

X. Gao and S. Guo are with IQE RF LLC, Somerset, NJ 08873 USA (e-mail: xgao@iqep.com; sguo@iqep.com).

Color versions of one or more of the figures in this letter are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/LED.2010.2095494

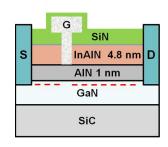

Fig. 1. Schematic cross section of gate-recessed E-mode InAlN/AlN/GaN HEMTs.

as other reliability problems [6]. Several approaches, including gate dielectric insertion [6], O<sub>2</sub> plasma treatment [7] and CF<sub>4</sub> plasma treatment [8] underneath the gate, and oxidefilled isolation followed by postgate annealing [9], showed gate leakage current reduction and an ON/OFF current ratio of up to ~10<sup>8</sup>-10<sup>9</sup> in depletion-mode AlGaN/GaN HEMTs. In enhancement-mode (E-mode) devices, the gate leakage current is usually more severe because of thinner barrier layers.

In this letter, E-mode InAlN/AlN/GaN HEMTs have been fabricated by selectively etching away the InAlN barrier in the gate region. Postprocessing annealing was performed to study the effect on gate leakage current and threshold voltage. After postprocessing annealing, an extremely low gate leakage current of  $\sim 10^{-12}$  A/mm, a record high ON/OFF current ratio of  $\sim 10^{12}$ , a positive threshold voltage shift, and a peak transconductance increase have been observed.

## **II. EXPERIMENTS**

The InAlN/AlN/GaN HEMT structure (Fig. 1) consists of a 4.8-nm InAlN barrier, a 1-nm AlN spacer, an unintentionally doped GaN channel, and a 1.8- $\mu$ m Fe-doped GaN semiinsulating buffer on SiC substrate, grown by MOCVD at IQE RF LLC. The devices were fabricated at Triquint Semiconductor, Inc., using the AlGaN/GaN HEMT process flow. Nitrogen ion implantation was used for isolation. Unoptimized Ti-based alloy ohmic contact gave a contact resistance  $R_c$  of  $\geq 0.55\Omega \cdot$  mm. The gate recess to etch away InAlN down to the AlN layer was realized by a BCl<sub>3</sub>-based reactive ion etching process following etching of the top SiN passivation using F-based plasma. Electron-beam lithography was used to define 150-nm-long gates with varying gate widths, followed by Pt/Au Fig. 2. (a) Linear-scale transfer curves at  $V_{\rm ds} = 6$  V and (b) common source family I-V values before and after postprocessing annealing, respectively.

gate metal deposition, and an additional 200-nm SiN passivation. The Hall-effect measurement using the Van der Pauw pattern in an unrecessed region shows a sheet resistance of  $\sim 270 \ \Omega/sq$ , a 2-DEG density of  $\sim 2 \times 10^{13} \ cm^{-2}$ , and an electron mobility of  $\sim 1160 \ cm^2/V \cdot s$ . More detailed descriptions on dc and RF characteristics of the E-mode HEMTs processed in the same manner have been reported elsewhere [10]. The devices presented here showed lower  $g_m$  due to higher  $R_c$  and likely higher density of interface states  $D_{it}$ .

The as-processed devices were annealed in forming gas (5%  $H_2$ , balanced with Ar) at 400 °C for 10 min, using a rapid thermal annealing system. Field-effect measurements were performed using a Keithley 4200 semiconductor characterization system at room temperature (RT), before and after postprocessing annealing.

### **III. RESULTS AND DISCUSSION**

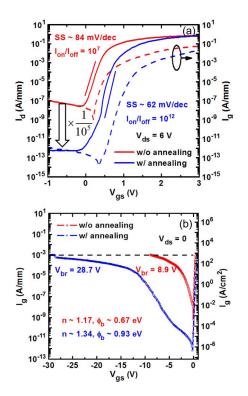

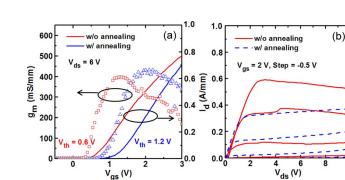

Shown in Fig. 2 are linear-scale transfer curves and common source family of I-V curves before and after postprocessing annealing, respectively. The device source-drain spacing is 2  $\mu$ m with a gate width of 8 × 50  $\mu$ m. Before postprocessing annealing, the peak extrinsic transconductance  $g_{m,\text{ext}}$  is 390 mS/mm at  $V_{\rm ds} = 6$  V, and the output drain current density is 0.78 A/mm at  $V_{\rm gs} = 3$  V. After postprocessing annealing, the transistor threshold voltage  $V_{\rm th}$  shifts from 0.6 to 1.2 V, extracted from the linear extrapolation of  $I_d$ ; meanwhile, the peak  $g_{m,\text{ext}}$  increases to 420 mS/mm. More than eight chips of devices from the same wafer were individually annealed and compared; the positive threshold voltage shift ( $\sim 0.2 -$ 0.6 V) has been observed in all the devices, and the device  $f_t/f_{\rm max}$  was found to improve by ~10%. Two chips were also annealed in N2 under otherwise the same conditions, and a similar trend in device performance improvement has been observed.

The common trend of a shift in  $V_{\rm th}$  shift and increase in peak  $g_{m,\rm ext}$  after postprocessing annealing was reported first in Pt-gated InAlAs HEMTs [11] and, more recently, in Ir-gated E-mode InAlN/AlN/GaN HEMTs [12]. Chen *et al.* [11] explained this phenomenon based on the previously reported studies on chemical reaction of Pt gate with underlying InAlAs: Upon annealing, InAlAs barrier was consumed, and conducting PtAs<sub>2</sub> was formed on a possible AlAs interface layer [13] on top of the thinned InAlAs barrier. Ostermaier *et al.* [12] postulated based on their transmission electron microscopic (TEM) studies

that the oxygen-bearing interface layer between gate metal Ir and InAlN became thinner upon annealing due to oxygen diffusion into Ir instead of Ir alloying with InAlN. Both processes have been termed as gate sinking, but due to different processes. In our case, on a separate process-control-monitoring chip, it was observed that  $R_c$  increased from 0.55 to 0.75  $\Omega \cdot \text{mm}$  after postprocessing annealing, while the access resistance did not change based on the Hall-effect measurement. Therefore, the increase of peak  $g_{m,ext}$  should stem from gate barrier thinning electrically, which could be due to physical gate sinking and/or interface state D<sub>it</sub> reduction. Our preliminary TEM study [10] shows that the 1-nm-thick AlN barrier under the Pt gate is continuous; however, an interface layer could exist [14], possibly consisting of residual InAlN and oxygen-bearing materials. Similar to Ostermaier's observations, this interlayer may have become thinner and denser upon thermal annealing, thus leading to physical "gate sinking."

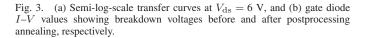

Fig. 3(a) shows semi-log-scale transfer curves measured at  $V_{\rm ds} = 6$  V. The gate leakage currents in both reverse and forward directions decrease after postprocessing annealing with an electrically thinner barrier. In the reverse bias direction, the gate leakage current decreasing from  $10^{-7}$  to  $10^{-12}$  A/mm is shown in Fig. 3(a), leading to an ON/OFF current ratio of  $10^{12}$ . To the best of our knowledge, this ON/OFF current ratio is the highest, accompanied by the lowest gate leakage current reported for any GaN-based transistor. In the forward bias direction, the turn-on voltage of gate diodes increases. Moreover, the subthreshold slope (*SS*) decreases from 84 to 62 mV/dec, which is very close to the theoretical limit at 300 K. One can extract the associated interface states from the *SS*

values [10] as  $1.5 \times 10^{13}$  and  $1.1 \times 10^{12}$  cm<sup>-2</sup>eV<sup>-1</sup> before and after postprocessing annealing, respectively. This indicates that the interface states that are possibly caused by the plasma treatment during the gate recess process have been repaired by the thermal treatment. It is also noted that the kinks observed in the *I*–*V* values of as-fabricated devices, shown in Fig. 2(b), disappeared upon annealing, suggesting these kinks are most likely related to traps.

Shown in Fig. 3(b), the gate diode breakdown voltage at  $I_g = 1$  mA/mm increases from 8.9 to 28.7 V after annealing; the three-terminal device breakdown voltages measured at  $I_d = 1$  mA/mm and  $V_{\rm gs} = -1$  V are the same, ~29 V. From the forward biased gate diode I-V characteristics, the effective thermionic barrier height of 0.67/0.93 eV and the ideality factor 1.17/1.34 are extracted before and after annealing, respectively. The extracted effective barrier heights are smaller than expected [10] due to tunnelling currents. Nevertheless, it implies that barrier height increase is one possibility for the observed electrically more insulating and thinner barrier.

Due to the large Schottky barrier height and ultrathin barrier, tunnelling current is the main leakage current mechanism, including both trap-assisted tunnelling (TAT) and direct Fowler–Nordheim tunnelling (FNT). The leakage current density caused by TAT can be expressed as [15]

$$J_{\text{TAT}} \propto N_t E_{\text{die}} \exp\left[-(\varepsilon_T - A\sqrt{E_{\text{die}}})/k_B T\right]$$

(1)

in which  $N_t$  is the trap density,  $E_{die}$  is the electrical field in the dielectric,  $\varepsilon_T$  is the trap energy below the dielectric conduction band edge, and A is a constant. Reduction in trap density can lead to gate leakage current reduction. The leakage current density caused by FNT can be expressed as [16]

$$J_{\rm FNT} = B E_{\rm die}^2 \exp\left(-C\phi_b^{3/2}/E_{\rm die}\right) \tag{2}$$

in which  $\phi_b$  is the barrier height (in eV), and *B*, *C* are positive constants. A larger barrier height due to possible formation of interface Al<sub>2</sub>O<sub>3</sub> or other insulators upon annealing can lead to gate leakage reduction. However, further work is necessary to gain a better picture of this interface.

## **IV. CONCLUSION**

The effect of postprocessing annealing on gate leakage current in gate-recessed E-mode InAlN/AlN/GaN HEMTs has been investigated. The record high ON/OFF current ratio of  $10^{12}$  with a very low leakage current of  $10^{-12}$  A/mm has been demonstrated, probably due to interface TAT weakening, Schottky barrier height increase, and ultrathin oxide formation. The positive threshold voltage shift (~0.6 V) and intrinsic peak transconductance increase (~23%), indicating barrier thinning

electrically, are attributed to  $D_{\rm it}$  reduction, barrier height increase, and, perhaps, physical gate sinking during postprocessing annealing.

#### REFERENCES

- H. Wang, J. W. Chung, X. Gao, S. Guo, and T. Palacios, "High performance InAlN/GaN HEMTs on SiC substrate," in *Proc. CS MANTECH Conf. Dig.*, 2010, pp. 185–188.

- [2] F. Medjdoub, J.-F. Carlin, M. Gonschorek, E. Feltin, M. A. Py, D. Ducatteau, C. Gaquiere, N. Grandjean, E. Kohn, "Can InAlN/GaN be an alternative to high power/high temperature AlGaN/GaN devices?" in *IEDM Tech. Dig.*, 2006, pp. 1–4.

- [3] H. Sun, A. R. Alt, H. Benedickter, E. Feltin, J.-F. Carlin, M. Gonschorek, N. R. Grandjean, and C. R. Bolognesi, "205-GHz (Al, In)N/GaN HEMTs," *IEEE Electron Device Lett.*, vol. 31, no. 9, pp. 957–959, Sep. 2010.

- [4] C. Sanabria, A. Chakraborty, H. Xu, M. J. Rodwell, U. K. Mishra, and R. A. York, "The effect of gate leakage on the noise figure of AlGaN/GaN HEMTs," *IEEE Electron Device Lett.*, vol. 27, no. 1, pp. 19–21, Jan. 2006.

- [5] W. Saito, M. Kuraguchi, Y. Takada, K. Tsuda, I. Omura, and T. Ogura, "High breakdown voltage undoped AlGaN-GaN power HEMT on sapphire substrate and its demonstration for DC–DC converter application," *IEEE Trans. Electron Devices*, vol. 51, no. 11, pp. 1913–1917, Nov. 2004.

- [6] V. Adivarahan, J. Yang, A. Koudymov, G. Simin, and M. A. Khan, "Stable CW operation of field-plated GaN-AlGaN MOSHFETs at 19 W/mm," *IEEE Electron Device Lett.*, vol. 26, no. 8, pp. 535–537, Aug. 2005.

- [7] J. W. Chung, J. C. Roberts, E. L. Piner, and T. Palacios, "Effect of gate leakage in the subthreshold characteristics of AlGaN/GaN HEMTs," *IEEE Electron Device Lett.*, vol. 29, no. 11, pp. 1196–1198, Nov. 2008.

- [8] R. Chu, L. Shen, N. Fichtenbaum, D. Brown, S. Keller, and U. K. Mishra, "Plasma treatment for leakage reduction in AlGaN/GaN and GaN Schottky contacts," *IEEE Electron Device Lett.*, vol. 29, no. 4, pp. 297–299, Apr. 2008.

- [9] Y. Lin, Y. Lain, and S. S. H. Hsu, "AlGaN/GaN HEMTs with low leakage current and high ON/OFF current ratio," *IEEE Electron Device Lett.*, vol. 31, no. 2, pp. 102–104, Feb. 2010.

- [10] R. Wang, P. Sanier, X. Xing, C. Lian, X. Gao, S. Guo, G. Snider, P. Fay, D. Jena, and H. Xing, "Gate-recessed enhancement-mode InAlN/AlN/GaN HEMTs with 1.9 A/mm drain current density and 800 mS/mm transconductance," *IEEE Electron Device Lett.*, vol. 31, no. 12, pp. 1383–1385, Dec. 2010.

- [11] K. J. Chen, T. Enoki, K. Maezawa, K. Arai, and M. Yamamoto, "High performance InP-based enhancement-mode HEMTs using non-alloyed ohmic contacts and Pt-based buried-gate technologies," *IEEE Trans. Electron Devices*, vol. 43, no. 2, pp. 252–257, Feb. 1996.

- [12] C. Ostermaier, G. Pozzovivo, B. Basnar, W. Schrenk, M. Schmid, L. Tóth, B. Pécz, J.-F. Carlin, M. Gonschorek, N. Grandjean, G. Strasser, D. Pogany, and J. Kuzmik, "Metal-related gate sinking due to interfacial oxygen layer in Ir/InAlN high electron mobility transistors," *Appl. Phys. Lett.*, vol. 96, no. 26, p. 263 515, Jul. 2010.

- [13] A. Fricke, G. Stareev, T. Kummetz, D. Sowada, J. Mahnss, W. Kowalsky, and K. J. Ebeling, "1.09-eV Schottky barrier height of nearly ideal Pt/Au contacts directly deposited on n- and p<sup>+</sup>n-A1<sub>0.48</sub>In<sub>0.52</sub>As layers," *Appl. Phys. Lett.*, vol. 65, no. 6, pp. 755–757, Aug. 1994.

- [14] S. Singhal, J. C. Roberts, P. Rajagopal, T. Li, A. W. Hanson, R. Therrien, J. W. Johnson, I. C. Kizilyalli, and K. J. Linthicum, "GaN-on-Si failure mechanisms and reliability improvements," in *Proc. IRPS*, 2006, pp. 95–98.

- [15] P. Rottlander, M. Hehn, and A. Schuhl, "Determining the interfacial barrier height and its relation to tunnel magnetoresistance," *Phys. Rev. B, Condens. Matter*, vol. 65, no. 5, p. 054 422, Jan. 2002.

- [16] K. Roy, S. Mukhopadhyay, and H. Mahmoodi-Meimand, "Leakage current mechanisms and leakage reduction techniques in deepsubmicrometer CMOS circuits," *Proc. IEEE*, vol. 91, no. 2, pp. 305–327, Feb. 2003.