# Perspectives of TFETs for low power analog ICs

Berardi Senale-Rodríguez, Yeqing Lu, Patrick Fay, Debdeep Jena, Alan Seabaugh, and Huili Grace Xing Department of Electrical Engineering University of Notre Dame

Notre Dame IN 46556 – USA bsensale@nd.edu, hxing@nd.edu

Abstract— In this paper we show that tunnel field effect transistors (TFETs) biased in the subthreshold region promise several advantages for low-power/high-frequency analog IC applications (e.g. GHz operation with sub-0.1 mW power consumption). Analytical and TCAD models for graphene nanoribbon (GNR) and InAs/GaSb nanowire TFETs are employed, respectively, for the first time in subthreshold analog circuit examples using the  $g_m/I_d$  integrated circuit (IC) design technique. From comparison of these TFET technologies with traditional FETs it is observed that due to the higher currents per unit gate width at low voltage for TFETs, smaller, higher speed, and lower power analog circuits are enabled.

*Index Terms*— TFET, low-power electronics, analog circuits, sub-threshold, design space exploration, graphene.

#### I. INTRODUCTION

Although there is significant research dealing with the advantages of TFETs for digital circuits [1], the benefits of employing these devices in analog applications, besides the possibility of operating at lower  $V_{DD}$  (< 0.1 V), have remained largely unexplored until recently [2]. Low power circuit design often requires transistors to operate in the regions where they are more efficient as generators of transconductance hence bandwidth, i.e. in the subthreshold region [3]. In this context, a usual parameter of interest for analog IC designers is the  $g_m/I_d$ ratio [4]. Due to the possibility of achieving < 60 mV/decade subthreshold swing [1], [5], TFETs can outperform traditional FETs in transconductance generation efficiency; the  $g_m/I_d$  ratio in traditional FETs is theoretically limited to  $< 1/nU_t < 38.5 \text{ V}^{-1}$ at room temperature (where n is the subthreshold slope factor and  $U_t$  the thermal voltage), whereas TFETs promise  $g_m/I_d >>$ 100 V<sup>-1</sup>. Using two example circuits: an intrinsic amplifier and a Miller operational transconductance amplifier (OTA) [6], the promised performance of two TFET technologies (GNR nanoribbon and InAs/GaSb nano-wire based) for low power analog applications is compared and discussed.

## II. TFETS

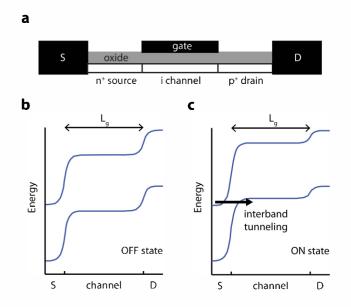

III. Shown in Fig. 1 is a schematic device cross section and a pair of energy band diagrams illustrating the operation principle of the *p*-TFET. With zero volts applied to the gate the transistor is off (Fig. 1b), the channel is fully-depleted so that tunneling from source to channel is prohibited. With

Leonardo Barboni and Fernando Silveira

Instituto de Ingeniería Eléctrica

Facultad de Ingeniería

Universidad de la República

Julio Herrera y Reissig 565, Montevideo 11300 – Uruguay

Ibarboni@fing.edu.uy, silveira@fing.edu.uy

negative voltage applied to the gate (Fig. 1c) electrons can tunnel from source to channel. Since the current turn-on mechanism in TFETs is by interband tunneling rather than by thermionic emission as in traditional FETs, the subthreshold swing is not limited to 60 mV/decade at room temperature.

Fig. 1. Cross section of a GNR TFET (a) and energy band diagram when the device is biased in (a) ON and (b) OFF-state. Figure adapted from [5].

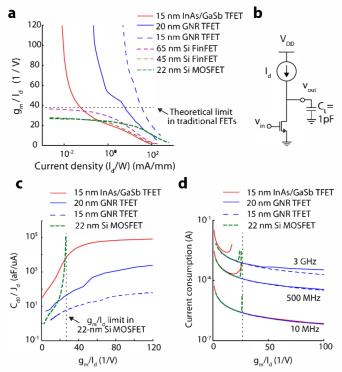

GNR TFETs were simulated as in [5] with gate lengths of 20 and 15 nm, ribbon widths of 3 and 2 nm, and 0.6 and 0.5 nm equivalent-oxide thickness (EOT). InAs/GaSb nanowire TFETs with 15 nm gate-length, 0.6 nm EOT, and 3.5 nm diameter were simulated using Synopsis TCAD. In analogy to traditional FETs, the  $g_m/I_d$  ratio was found to be weakly dependent on  $V_{ds}$  for a fixed  $V_{gs}$  (figure not shown), which allows for the use of the  $g_m/I_d$  design methodology [4]. Shown in Fig. 2a is  $g_m/I_d$  as a function of current per unit width  $J_d = I_d/W$  for the analyzed TFET technologies, and several MOSFET and FinFET technologies [7], [8]. GNR TFETs should provide superior current drive relative to other TFET technologies. Moreover, as also pictured in Fig. 2a, the subthreshold region current densities in the GNR TFETs for a given  $g_m/I_d$  ratio are larger than those attainable in comparable

gate length traditional FETs (e.g. 22-nm Si MOSFET technology [7]).

Fig. 2. (a)  $g_m/I_d$  as a function of drain current density. (b) Schematic circuit of an intrinsic amplifier. (c)  $C_{d0}/I_d$  as a function of  $g_m/I_d$ . (d) Current consumption versus  $g_m/I_d$  for different target gain-bandwidth product (*GBW*) values in an intrinsic amplifier ( $C_L = 1$ pF is assumed)

# IV. EXAMPLE CIRCUITS

## A. Intrinsic Amplifier

An intrinsic amplifier, consisting of a current biased transistor in a common source configuration loaded by a capacitance  $C_{L_i}$  is shown in Fig. 2b [4]. In this configuration, the current consumption (as a function of the transistor  $g_m/I_d$ ) can be expressed as:

$$I_{d} = \frac{2\pi \times GBW \times C_{L}}{\frac{g_{m}}{I_{d}} - 2\pi \times GBW \times \frac{C_{d}}{J_{d}}},$$

(1)

where gain-bandwidth product (*GBW*) and  $C_L$  are set by the design requirements, and  $J_d$  and  $C_{d0}$  are functions of  $g_m/I_d$  (see Fig. 2a and 2c).  $C_d$  is defined as the capacitance seen from the transistor drain to ground in the absence of load capacitance (i.e. the capacitance that adds to  $C_L$ ), and  $C_{d0} = C_d/W = (C_{gd} + C_{bd})/W$  in traditional FETs (where  $C_{bd}$  is the bulk-to-drain capacitance) and approximately equal to  $C_{gd0}$  in TFETs (where  $C_{gd0}$  is the gate-to-drain capacitance per unit width).

When comparing current consumption for intrinsic amplifiers employing the two TFETs and the 22-nm Si CMOS, it is observed (Fig. 2c) that for low *GBW* requirements (e.g. 10 MHz) both TFETs promise lower current consumption than the CMOS because of the possibility of operating TFETs in the

subthreshold region with very large  $g_m/I_d$  (>38.5 V<sup>-1</sup>). Under this constraint of low *GBW*, the second term of the denominator in Eq.(1) is small so current consumption is a monotonically decreasing function of  $g_m/I_d$ . Thus, the most power efficient technologies are the ones able to achieve the largest  $g_m/I_d$ .

The current consumption increases with increasing GBW (Fig. 2b). For high GBW (i.e. 3 GHz), the key to minimize current consumption is to employ a technology with high  $g_m/I_d$ while keeping  $C_{d0}/J_d$  as low as possible, as dictated by the denominator of Eq. (1). To this end, we plot  $C_{d0}/J_d$  vs.  $g_m/I_d$  in Fig. 2c for various transistor technologies, where the advantages of the GNR TFET become more evident. In this case, for a given  $g_m/I_d$ , because of the larger attainable  $J_d$  in the GNR TFET, the second term in the denominator of Eq. (1) is smaller for the GNR TFETs even though TFETs tend to higher  $C_{ed0}$  than conventional FETs [9]. For instance, at a GBW of 3 GHz, lower current consumption (>2 times) can be obtained by employing GNR TFETs in comparison to the other technologies. In addition, the GNR TFETs allow for the smallest device areas for a given design specification due to their superior current drives  $(J_d)$  for a given  $g_m/I_d$ .

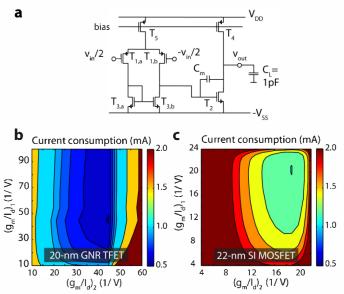

Fig. 3. Schematic circuit of a Miller OTA (a). And design space exploration for GBW = 1 GHz and PM =  $60^{\circ}$  employing: (b) 20-nm GNR TFETs, and (c) 22-nm Si MOSFETs. Current consumption for the optimal design employing GNR TFETs is about the minimum theoretically achievable in this circuit if employing ideal traditional FETs ( $C_s = C_g = C_d = 0$ ), which is >2X lower than the minimum achievable in the 22-nm Si MOSFET technology.

## B. Miller OTA

A Miller OTA shown in Fig. 3a is analyzed employing n and p-type 20-nm GNR TFETs as well as 22-nm Si MOSFETs. GNR TFETs are chosen over other TFETs because of their large subthreshold current densities, but also because they provide similar characteristics for both n and p-type transistors resulting from the symmetric band structure of graphene [5, 10], which is desirable for circuit design.

This amplifier topology has two poles and a right half plane zero; usual requirements for more than  $60^{\circ}$  phase margin (PM) in this circuit are: NDP = 2.2, Z = 10, where  $NDP = \omega_{p2} / GBW$  ( $\omega_{p2}$  is the frequency of the non dominant pole), and  $Z = \omega_z / GBW$  ( $\omega_z$  is the frequency of the zero). The current consumption in this amplifier can be expressed as:

$$I = 2I_{d1} + I_{d2} = 2\frac{GBW \times C_m}{(g_m / i_d)_1} + \frac{Z \times GBW \times C_m}{(g_m / i_d)_2}, \quad (2)$$

where  $I_{dl}$  is the DC current through the transistors at the input differential pair  $(T_{1a}, T_{1b})$ ,  $I_{d2}$  is the current through the transistor at the output stage  $(T_2)$ , and  $C_m$  is the Miller compensation capacitance, which is calculated as:

$$C_{m} = \frac{NDP}{2Z} \left( C_{1} + C_{2} + \sqrt{\left(C_{1} + C_{2}\right)^{2} + \frac{4Z \times C_{1} \times C_{2}}{NDP}} \right), \quad (3)$$

where  $C_2 = C_{out} + C_L$  is the total output capacitance of the amplifier ( $C_{out}$  is the capacitance seen looking from the node  $V_{out}$  to ground in the absence of load capacitance), and  $C_I$  is the effective capacitance from the gate of  $T_2$  to the AC ground.

From Eqn. (2) and (3), we find that the minimum achievable current consumption in ideal traditional FETs based Miller OTA, i.e. the current consumption considering the transistors with zero capacitances and maximum  $g_m/I_d$ , is thus given by:

$$I = \frac{(2+Z) \times GBW \times U_T \times C_L \times NDP}{Z},$$

(4)

The synthesis mechanism described in Ref. [6] was employed to determine the amplifier design achieving the minimum current consumption. For a 500 MHz GBW and 60° PM design requirements, the optimal current consumption employing the 20-nm-gate GNR TFETs was found to be 35% smaller than the minimum theoretically achievable by ideal traditional FETs under the same design constraints, Eq. (4). When setting the GBW requirement to 1GHz, the current consumption employing GNR TFETs was found to be about the minimum theoretically achievable in this circuit if employing ideal traditional FETs (2% lower). Moreover, when comparing the current consumption with respect to that achievable employing a similar gate-length Si-FET technology (22-nm), we see that the current consumption of the Miller OTA with GNR TFETs can be > 2X smaller, i.e. the minimum achievable current consumption in the GNR/Si-MOSFET amplifiers is  $\sim 0.5/1.2$  mA, respectively (Fig. 3b-c).

## V. CONCLUSION

Since TFETs can operate in the sub-threshold region with larger  $g_m/I_d$  than traditional FETs, low power analog circuits with lower current consumption can be designed. In particular, GNR TFETs promise large bandwidth at low voltage drive due to their high current density in the subthreshold region. Based on this analysis, GNR TFETs seem to be very promising among all the field effect transistors proposed to date for ultralow power analog applications.

## **ACKNOWLEDGMENT**

The authors will like to acknowledge the support from the Midwest Institute for Nanoelectronics Discovery (MIND) at the University of Notre Dame and from CSIC of Universidad de la República.

## REFERENCES

- A. Seabaugh and Q. Zhang, "Low-voltage tunnel transistors for beyond CMOS logic," *Proceedings of the IEEE*, vol. 98, no. 12, pp. 2095 –2110, 2010.

- [2] A. Mallick and A. Chattopadhyay, "Tunnel Field-Effect Transistors for Analog/Mixed-Signal System-on-Chip Applications". *IEEE Trans. Electron Dev.*, vol. 59, no. 4, pp. 888-894, 2012.

- [3] E. Vittoz and J. Fellrath, "CMOS Analog Integrated Circuits Based on Weak Inversion Operation," *IEEE J. of Solid-State Circuits*, vol. 12, no. 3, pp. 224-231, June 1977.

- [4] F. Silveira, D. Flandre, and P. G. A. Jespers, "A gm/ID based methodology for the design of CMOS analog circuits and its application to the synthesis of a silicon-on-insulator micropower OTA," *IEEE J. Solid-State Circuits*, vol. 31, p. 1314, Sept. 1996.

- [5] Q. Zhang, T. Fang, H. Xing, A. Seabaugh, and D. Jena, "Graphene nanoribbon tunnel transistors," *IEEE Electron Device Lett.*, vol. 29, no. 12, pp. 1344–1346, Dec. 2008.

- [6] P. Aguirre and F. Silveira, "CMOS op-amp power optimization in all regions of inversion using geometric programming" in *Proc. SBCCI*, pp. 152-157, 2008.

- [7] W. Zhao and Y. Cao, "Predictive technology model for nano-CMOS design exploration", ACM J. Emerging Technol. Comput. Syst., vol. 3, no. 1, pp. 1–17, Apr. 2007.

- [8] B. Parvais, A. Mercha, N. Collaert, R. Rooyackers, I. Ferain, M. Jurczak, V. Subramanian, A. De Keersgieter, T. Chiarella, C. Kerner, L. Witters, S. Biesemans and T. Hoffman "The device architecture dilemma for CMOS technologies: Opportunities and challenges of FinFET over planar MOSFET", Proc. Symp. VLSI Technol., Syst. Appl., pp.80-81, 2009.

- [9] S. Mookerjea, R. Krishnan, S. Datta, and V. Narayanan, "On enhanced Miller capacitance effect in interband tunnel transistors," *IEEE Electron Device Lett.*, vol. 30, no. 10, pp. 1102–1104, Oct. 2009.

- [10] K. S. Novoselov, A. K. Geim, S. V. Morozov, D. Jiang, M. I. Katsnelson, I. V. Grigorieva, S. V. Dubonos, and A. A. Firsov, "Twodimensional gas of Dirac fermions in graphene," *Nature*, vol. 438, no. 7065, pp. 197–200,Nov. 2005.