## 1230 V β-Ga<sub>2</sub>O<sub>3</sub> trench Schottky barrier diodes with an ultra-low leakage current of <1 $\mu$ A/cm<sup>2</sup>

Wenshen Li,<sup>1,a)</sup> Zongyang Hu,<sup>1</sup> Kazuki Nomoto,<sup>1</sup> Zexuan Zhang,<sup>1</sup> Jui-Yuan Hsu,<sup>2</sup> Quang Tu Thieu,<sup>3</sup> Kohei Sasaki,<sup>3</sup> Akito Kuramata,<sup>3</sup> Debdeep Jena,<sup>1,2,4</sup> and Huili Grace Xing<sup>1,2,4,a)</sup>

<sup>1</sup>School of Electrical and Computer Engineering, Cornell University, Ithaca, New York 14853, USA

<sup>2</sup>Department of Material Science and Engineering, Cornell University, Ithaca, New York 14853, USA

<sup>3</sup>Novel Crystal Technology, Inc., Sayama 350-1328, Japan

<sup>4</sup>Kavli Institute at Cornell for Nanoscale Science, Cornell University, Ithaca, New York 14853, USA

(Received 16 August 2018; accepted 30 October 2018; published online 13 November 2018)

$\beta$ -Ga<sub>2</sub>O<sub>3</sub> vertical trench Schottky barrier diodes (SBDs) are realized, demonstrating superior reverse blocking characteristics than the co-fabricated regular SBDs. Taking advantage of the reduced surface field effect offered by the trench metal-insulator-semiconductor structure, the reverse leakage current in the trench SBDs is significantly suppressed. The devices have a higher breakdown voltage of 1232 V without optimized field management techniques, while having a specific on-resistance (R<sub>on,sp</sub>) of 15 m $\Omega$  cm<sup>2</sup>. An ultra-low leakage current density of <1  $\mu$ A/cm<sup>2</sup> is achieved before breakdown, the lowest among all reported Ga<sub>2</sub>O<sub>3</sub> Schottky barrier diodes. Fast electron trapping and slow de-trapping near the Al<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> interface are observed by repeated C-V measurements, which show an interface state ledge and positive shifts of flat-band voltages with increasing voltage stress. By comparison between pulsed and DC measurements, the device self-heating effect and the trapping effect are uncoupled. It is found that the trapping effect at the trench sidewall affects the on-resistance of the trench SBDs, even under pulsed conditions. With reduced trapping effect and better field management technique, the trench SBDs could further harvest the promising material properties of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>. *Published by AIP Publishing*. https://doi.org/10.1063/1.5052368

$\beta$ -Ga<sub>2</sub>O<sub>3</sub> has become an attractive material for the development of electronic devices that benefit from the high expected critical electric field of ~8 MV/cm,<sup>1</sup> as a result of its wide bandgap (~4.5 eV),<sup>2</sup> as well as the decent electron mobility of ~200 cm<sup>2</sup>/V s at room temperature.<sup>3–5</sup> Such devices include power electronic devices<sup>6–22</sup> and scaled RF power amplifiers,<sup>23–25</sup> especially in a high temperature harsh environment.<sup>26</sup> On top of the attractive material properties, the availability of melt-growth methods to mass-produce single crystal bulk substrates<sup>27</sup> provides important benefits towards low cost as well as the fast development of device technologies and epitaxial growth.

The attractiveness of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> for power electronic devices arises from its highly projected Baliga's figure-of-merit (FOM).<sup>1</sup> In recent years, fast progress on the performance of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>-based power devices has been made. A critical electric field of up to 5.2 MV/cm (Refs. 8 and 28) has been observed. With the help of the field-plate, lateral transistors with a breakdown voltage (BV) of 750 V<sup>7</sup> and Schottky barrier diodes with a BV over 1 kV (Refs. 16–19, 21, and 22) have been demonstrated. With the employment of a trench or vertical-fin structure, enhancement-mode transistors with over 1 kV breakdown voltage and decent on-resistance (R<sub>on</sub>) have been realized.<sup>12</sup> As a result of such advancements, a FOM (BV<sup>2</sup>/R<sub>on</sub>) higher than Si has been achieved.

To further improve the FOM in Ga<sub>2</sub>O<sub>3</sub> power devices, the electric field profile needs to be carefully managed to prevent

premature breakdown due to field crowding. In addition, in the case of Schottky barrier diodes, reduced surface field (RESURF) techniques are necessary, since the high electric field at the Schottky contact will induce high reverse leakage current through thermionic field emission and image-force-induced barrier lowering effect. Among various RESURF techniques, a trench metal-insulator-semiconductor (MIS) structure<sup>29</sup> is desirable for  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> since it does not require a conductive p-type region, which is yet to be realized in Ga<sub>2</sub>O<sub>3</sub>. In early days, such vertical devices employing castellated surface structures were often termed as *trench* Schottky barrier diodes (SBDs)<sup>29</sup> or static induction transistors (SITs)<sup>30</sup> in Si, SiC, etc.; more recently, device names referring to trenches as *fins* were also adopted in GaN<sup>31</sup> and  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>.<sup>12,32</sup> Thus, in this context, we will use trench and fin interchangeably.

The first demonstrations of Ga<sub>2</sub>O<sub>3</sub> trench-MIS SBDs<sup>20,21</sup> have been very recently reported; however, the FOM is poorer than that of the regular SBDs limited by the device design coupled with the wafer quality. In this work, we report an ultra-low leakage current below 1  $\mu$ A/cm<sup>2</sup> in the Ga<sub>2</sub>O<sub>3</sub> trench SBDs as a definitive proof of the RESURF effect, as well as a state-of-the-art FOM, thanks to the improved epitaxial material with a uniform doping concentration of ~2 × 10<sup>16</sup> cm<sup>-3</sup>.

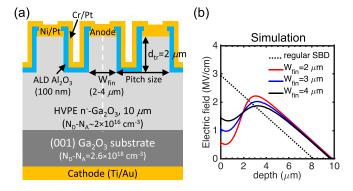

The schematic cross-section of the trench SBDs is shown in Fig. 1(a). The devices are fabricated on a (001)  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> n-type bulk substrate with a 10– $\mu$ m n<sup>-</sup> epitaxial drift layer grown by halide phase vapor epitaxy (HVPE) with a net doping concentration of ~2 × 10<sup>16</sup> cm<sup>-3</sup>. Vertical fins with widths (W<sub>fin</sub>) of 2, 3, and 4  $\mu$ m and a height of 2  $\mu$ m are designed. Between the fins is the trench region, where the

<sup>&</sup>lt;sup>a)</sup>Authors to whom correspondence should be addressed: wl552@cornell.edu and grace.xing@cornell.edu

FIG. 1. (a) Schematic cross-section of the  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> trench Schottky barrier diodes. Fin widths (W<sub>fin</sub>) of 2, 3, and 4  $\mu$ m are designed, along with a trench depth (d<sub>tr</sub>) of 2  $\mu$ m. (b) Simulated electric field profile at a reverse bias of 1200 V along vertical cut lines at the center of the fins [see the dashed line in (a)]. The electric field profile in a regular SBD is shown in the dotted line for comparison.

MIS-junction is located. The fin area ratio over the entire device area (or  $W_{fin}$ /pitch size) for all fin widths is  $(60 \pm 5)\%$ . Figure 1(b) shows the simulated electric field profile at a reverse bias of 1200 V along a vertical cutline in the center of the fin [see the dashed line in Fig. 1(a)]. In comparison with the regular SBD, the electric field near the top surface is effectively reduced by the trench-MIS structure and the RESURF effect is more pronounced with a smaller fin width.

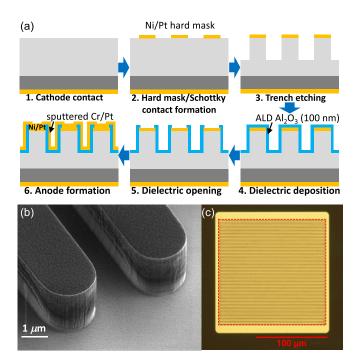

The fabrication process of the trench SBDs is illustrated in Fig. 2(a). First, reactive ion etch (RIE) based on BCl<sub>3</sub> and  $Ar^{33}$  was performed on the backside of the wafer to facilitate ohmic contact. After that, Ti (50 nm)/Au (125 nm) was evaporated on the backside as the cathode contact followed by a rapid thermal anneal (RTA) for 1 min in a N<sub>2</sub> environment.<sup>34</sup> Next, Ni (20 nm)/Pt (120 nm) was deposited and patterned by a lift-off process on the top surface, serving as the Schottky

FIG. 2. (a) Fabrication process flow of the trench- or fin-SBDs. (b)  $45^{\circ}$  tilted SEM image of the etched fins with a fin width of 2  $\mu$ m. (c) Optical graph of the top view of a fabricated device with a fin width of 2  $\mu$ m. *The central anode area enclosed by the red dashed line is used for calculating current densities.*

contact as well as the hard mask for the subsequent etching for trench formation. Trenches with a depth of  $2\,\mu$ m were etched using RIE, resulting in fin channels oriented along the [010] direction. Figure 2(b) shows a scanning electron microscopy (SEM) image of the etched fin channels tilted at 45°. Near vertical fin sidewalls are observed. Subsequently, the etched surface was cleaned in HCl before the deposition of a 100-nm Al<sub>2</sub>O<sub>3</sub> dielectric layer by atomic layer deposition (ALD). Next, the dielectric was opened by dry etching to expose the Ni/Pt Schottky contact, followed by a deposition of Cr (10 nm)/Pt (70 nm) over the sidewall by sputtering. Figure 2(c) shows a top-view optical image of a fabricated trench SBD with a fin width of 2- $\mu$ m. The cross-section SEM image of the device is shown in the supplementary material.

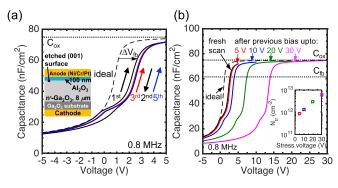

Under the same fabrication process, regular SBDs with the same Ni/Pt Schottky contact on the original epitaxial surface were also formed. A net doping concentration  $(N_D-N_A)$ of  $\sim 2 \times 10^{16}$  cm<sup>-3</sup> is extracted from the regular SBDs from capacitance-voltage (C-V) measurements (see supplementary material). With an additional evaporation of Ni (20 nm) on the planar surface prior to the sputtering of Cr/Pt, MOScapacitors with a Ni-based anode contact on the etched (001) surface were co-fabricated on the same sample. Figure 3 shows the high frequency C-V measurements on a MOScapacitor. To investigate the charge trapping effect typically seen at the MOS interface, repeated sweeps were performed on the capacitor starting with a fixed reverse bias limit of  $-30\,\mathrm{V}$  and toward different forward bias limits (stress voltage), which was stepped up from 5 V to 30 V. At each stress voltage, 3 repeated dual-direction sweeps were performed. Figure 3(a) shows the first set of sweeps up to a stress voltage of 5 V. In comparison with the ideal C-V curve, the 1st upward sweep shows a positive flat-band voltage (V<sub>fb</sub>) shift of 1.6 V as a result of an interface state ledge.<sup>35</sup> The ledge is due to the population of deep interface states with trapped electrons during the upward sweep. Assuming that the trapped charge is located close to the Al<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> interface, the sheet density of the trapped negative charge  $(N_{tr})$  can be obtained by

FIG. 3. High-frequency capacitance-voltage (C-V) measurements on a MOScapacitor fabricated on the etched (001) surface. The device cross-section is shown in the inset of (a). Repeated C-V sweeps were performed with a fixed reverse bias limit of -30 V and a different forward bias limit (stress voltage), which was stepped up from 5 V to 30 V. At each stress voltage, 3 repeated dual-direction sweeps were performed starting from -30 V. (a) The set of sweeps up to 5 V. The ideal C-V curve in the absence of the trapping effect is shown in the dashed line. (b) The 3rd upward sweeps at each forward bias limit and the inset shows a plot of the extracted trapped charge density (N<sub>tr</sub>) at each stress voltage. A probing frequency of 0.8 MHz and a sweep rate of 0.1 V/s were used for all sweeps. No hold time was employed.

$$N_{tr} = C_{ox} \cdot \Delta V_{fb} / e, \qquad (1)$$

where  $C_{ox}$  is the dielectric capacitance, *e* the elemental charge and  $\Delta V_{fb}$  the flat-band voltage shift. According to Eq. (1), a N<sub>tr</sub> of  $7.4 \times 10^{11} \text{ cm}^{-2}$  is calculated based on the  $\Delta V_{fb}$  of 1.6 V associated with the 1st upward sweep to 5 V. These trapped charges should be primarily due to the deep interface states. After the 1st sweep to 5 V, the V<sub>fb</sub> is further shifted as indicated by the hysteresis. The  $V_{\rm fb}$  shift is not recovered after the downward sweep back to deep depletion and stays nearly the same as indicated by the subsequent upward sweeps. On the other hand, the interface state ledge is nearly identical in subsequent upward sweeps. This indicates that the trapped charge associated with the ledge can be mostly de-trapped with the downward sweep but there are additional trapped charges that cannot be de-trapped, which suggests that trapping mechanisms other than the deep interface states may exist. Figure 3(b) shows the 3rd upward sweeps at each forward bias limits. The V<sub>fb</sub> increases with increasing bias limit, suggesting an increasing N<sub>tr</sub>. The V<sub>fb</sub> shift does not recover until several days later. Inset shows the extracted  $N_{tr}$  based on the  $\Delta V_{fb}$  referenced to the ideal C-V curve at each stress voltage. Notice that the interface state ledge is present in each upward sweep. It further suggests that the deep interface states associated with the C-V ledge is not the only trapping mechanism. In fact, such a charge trapping effect has been observed in several reports on Al<sub>2</sub>O<sub>3</sub>/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub> MOS capacitors, <sup>36–39</sup> and the traps inside the ALD Al<sub>2</sub>O<sub>3</sub> dielectric have been identified as one of the major causes.<sup>40</sup> We thus speculate that the increasing trapping effect or N<sub>tr</sub> with increasing voltage stress is likely associated with the traps in the dielectric. In addition, it is worth noting that N<sub>tr</sub> after the voltage stress toward accumulation (30 V) is  $\sim 5 \times 10^{12} \,\mathrm{cm}^{-2}$ , which is similar to the values reported in Refs. 36 and 38. As will be discussed later, the trapping effect is detrimental to the forward conduction of the trench SBDs.

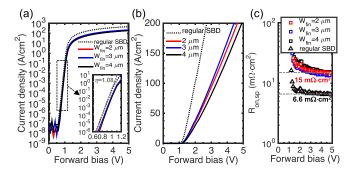

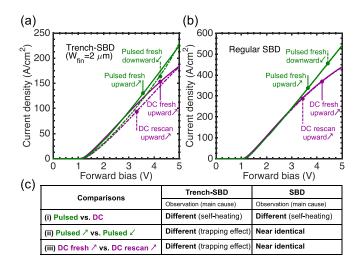

The forward I-V characteristics of the trench SBDs is compared with that of the regular SBDs in Figs. 4 and 5. Both DC and pulsed measurements were performed on the devices. For a fair comparison, the current density of the trench SBDs was calculated by the entire central area of the anode enclosed by the dashed line in Fig. 2(c). Figure 4(a) shows the DC measurement results in a log-scale. The trench

FIG. 4. Forward I-V characteristics of the trench SBDs in comparison with the regular SBD fabricated on the same wafer. (a) Measurements under DC conditions in a log scale. The inset shows the zoom-in plot of the exponential turn-on region. The ideality factor of the diodes is extracted to be  $\sim 1.08$ . (b) Measurements under pulsed conditions from 0 V to 5 V in a linear scale. The pulse width is 8.4  $\mu$ s and the duty cycle is 0.84%. The quiescent voltage (V<sub>Q</sub>) is 0 V. (c) Extracted differential specific on-resistance from pulsed I-V measurements.

SBDs and the regular SBD have the same ideality factor of 1.08. The barrier height ( $\phi_{\rm B}$ ) of the trench SBDs and the regular SBD is extracted to be 1.40 eV and 1.35 eV, respectively, using the thermionic emission model. The slightly higher barrier height/turn-on voltage in the trench SBDs was observed before both in trench SBDs<sup>20</sup> as well as in trench junction-barrier-Schottky-diodes,<sup>41</sup> which can be attributed to the increase of the effective barrier height due to the adjacent MOS junction or p-n junction.<sup>41</sup> Figure 4(b) shows the pulsed I-V measurements from 0V to 5V in a linear-scale. The pulsed I-V measurements were performed to mitigate primarily the self-heating effect, as will be discussed more in detail later. In comparison with the regular SBD, the trench SBDs have lower current density. This is due to the restricted conduction path as a result of the fin geometry. The current density for different fin widths is similar, and the finite variation is attributed to the slight difference in the fin area ratio, nonuniformity of the processing and the doping concentration in the wafer. Figure 4(c) shows the extracted specific differential on-resistance (Ron,sp) of the devices from the pulsed measurements. The trench SBDs have an  $R_{on,sp}$  of  $\sim 15 \text{ m}\Omega \text{ cm}^2$ , while the regular SBD has an  $R_{on,sp}$  of 6.6 m $\Omega$  cm<sup>2</sup>.

The comparisons between the DC and pulsed measurements under different measurement conditions are shown in Fig. 5. In the trench SBD [Fig. 5(a)], notable differences are observed in three sets of comparisons: (i) pulsed vs. DC scan; (ii) pulsed scan upward vs. pulsed scan downward and (iii) DC fresh scan vs. DC re-scan. In the regular SBD [Fig. 5(b)], notable difference is observed only in: (i) pulsed vs. DC scan. These comparisons are summarized in the table in Fig. 5(c). In the comparison (i) for the regular SBD, a lower current is observed under the DC scan at a bias higher than 3 V compared with the pulsed scan. This is attributed to the device self-heating effect under DC measurements. For the trench SBD, the difference in comparison (i) is similar to that in the regular SBD and is primarily due to the selfheating effect. However, distinct from the regular SBD, it is also compounded by the trapping effect as indicated by comparisons (ii) and (iii). In comparison (ii) for the trench SBD, the self-heating effect is removed by the pulsed condition. As a result, the difference between the pulsed upward and downward scans on a fresh trench SBD should be due to the presence of trapping effect. Since no trapping effect is observed in the regular SBDs, the trapping must be located at the trench MIS structure. Although the crystal orientation of the fin sidewall is different from that of the (001) surface, we speculate that the similar trapping effect occurs as in the MOS-capacitors on the etched (001) surface. That is, when a positive voltage is applied at the anode of the trench SBD, negative charges start to get trapped near the sidewall interface. The negative sheet charge causes a depletion of the fin channel. Assuming an  $N_{tr}$  of  ${\sim}8 \times 10^{11}\,\text{cm}^{-2}$  at the trench sidewall similar to the value extracted in the MOS-cap after a 5-V stress, there will be an extra depletion width of  $\sim$ 170 nm at zero bias in the channel from each side due to the N<sub>tr</sub>. The extra depletion width increases the channel resistance, thus lowering the measured current. Notice in comparison (ii) for the trench SBD, the downward pulsed scan measures a higher current initially at 5V than the upward pulsed scan. This is because no charge trapping

FIG. 5. Pulsed vs. DC I-V measurements (a) on a trench SBD with a fin width of  $2 \mu m$  and (b) on a regular SBD. (c) Summary of the three sets of comparisons among different measurement conditions.

occurred before the 5-V current data were first acquired during the downward scan. In contrast, the downward pulsed scan measures lower current than the upward pulsed scan between 1.5 and 4.5 V. This is due to a more pronounced charge trapping effect within this biasing region under the downward scan as a result of the initial biasing at 5V. Similarly, in comparison (iii) for the trench SBD, the lower current under the DC rescan is also due to the charge trapping after the device was biased at 5 V. Due to the asymmetry between the fast trapping process and the slow detrapping process, the pulsed measurement data for the trench SBD is still affected by the trapping effect and the extracted Ron,sp under the pulsed condition is still higher than the ideal Ron.sp determined by the intrinsic drift layer material property and the device geometry. The trapping effect could be reduced with a post deposition anneal (PDA) of the ALD dielectric<sup>40,42</sup> and with improved surface treatment on the etched Ga<sub>2</sub>O<sub>3</sub> surface after the dry etch.

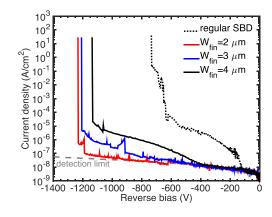

The representative reverse I-V characteristics of the trench SBDs in comparison with the regular SBD is shown in Fig. 6. In the regular SBD, the reverse leakage current increases quickly as the reverse bias is increased. The hard breakdown voltage is 734 V. In comparison, the trench SBDs have much lower leakage currents and higher BVs. In devices with a  $W_{fin}$  of 2  $\mu$ m, the highest BV of 1232 V is observed,

FIG. 6. Reverse bias I-V characteristics of the trench SBDs in comparison with the regular SBD.

together with an ultra-low leakage current density of less than 1  $\mu$ A/cm<sup>2</sup> before breakdown, without other optimized field management techniques. For a bias lower than ~1000 V, the leakage current density is around the detection limit (<0.1  $\mu$ A/cm<sup>2</sup>), translating into a very low off-state power dissipation of <0.1 mW/cm<sup>2</sup>. Higher leakage current and lower breakdown voltage is observed for wider fin widths, suggesting that a narrow fin width is preferable for a more pronounced RESURF effect and a higher breakdown voltage.

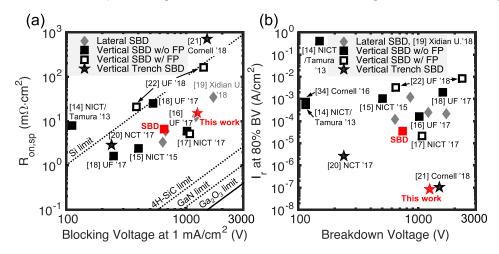

Figure 7(a) benchmarks the state-of-the-art  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> SBDs, using a reverse blocking voltage defined at  $1 \text{ mA/cm}^2$ , as typically used in commercial SBDs for a reasonable offstate power consumption. With such a definition, the FOM at  $1 \text{ mA/cm}^2$  for a number of regular SBDs is worse than using the hard breakdown voltage, especially for the SBDs with breakdown voltages higher than 1 kV, due to their high leakage current under high surface fields. Although not having the highest FOM at 1 mA/cm<sup>2</sup> among all the reported SBDs, the 2- $\mu$ m trench SBD from this work has a comparable FOM with the best SBDs, while achieving a notable improvement in the FOM compared with the previous trench SBD reports.<sup>20,21</sup> In comparison with our previous results,<sup>21</sup> the on-resistance is much reduced due to a more uniform doping profile with a moderate level ( $\sim 2 \times 10^{16} \text{ cm}^{-3}$ ) and less carrier compensation.

Figure 7(b) shows the leakage current density at 80% of the reported BV vs. the reported BV of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> SBDs. It can be seen that the trench SBDs generally have lower leakage currents than the regular SBDs. The 2- $\mu$ m trench SBDs

FIG. 7. Benchmark plots of the stateof-the-art  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> SBDs. (a) Differential specific on-resistance Ron,sp (excluding the turn-on voltage) vs. the blocking voltage specified at a reverse leakage current density of 1 mA/cm<sup>2</sup>. (b) Leakage current density at 80% of the reported BVs vs. the reported hard-breakdown voltage. The  $2-\mu m$  trench SBD in this work has the lowest leakage current at 80% BV among all the reported SBDs.

in this work achieve the lowest leakage current density among the reported  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> SBDs. Note that a number of reported vertical SBDs use similar HVPE-grown drift layers with a net doping concentration around  $2 \times 10^{16}$  cm<sup>-3</sup>.<sup>15–17</sup> As is expected, our regular SBD shows a comparable leakage level as those reports, suggesting that the observed advantage over the leakage current in our trench SBDs arises from the device structure itself.

In conclusion,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> vertical trench SBDs with pronounced RESURF effects and state-of-the-art FOM are reported. Fast electron trapping and slow de-trapping are observed near the Al<sub>2</sub>O<sub>3</sub>/Ga<sub>2</sub>O<sub>3</sub> interface from repeated C-V measurements. Comparing the forward I-V characteristics under DC versus pulsed conditions, it is found that device self-heating limits the DC current at >3 V and the trapping effect at the fin sidewall affects the measured on-resistance even under pulsed conditions. The trench SBD with a 2- $\mu$ m fin width is found to have a breakdown voltage of 1232 V and an ultra-low leakage current of <1  $\mu$ A/cm<sup>2</sup>, the lowest reported value among the reported  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> Schottky barrier diodes. The FOM could be further improved toward the promised material limit of  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> with a reduced trapping effect and better field management.

See supplementary material for more information on the device cross-section, doping profile and dielectric quality.

This work was supported in part by the NSF DMREF Program under a Grant 1534303 monitored by J. Schlueter and in part by AFOSR under a Grant FA9550-17-1-0048 monitored by K. Goretta and carried out at the Cornell Nanoscale Science and Technology Facilities (CNF) sponsored by the NSF NNCI program (ECCS-1542081). This work made use of the Cornell Center for Materials Research Shared Facilities which are supported through the NSF MRSEC program (DMR-1719875).

- <sup>1</sup>M. Higashiwaki, K. Sasaki, A. Kuramata, T. Masui, and S. Yamakoshi, Appl. Phys. Lett. **100**, 013504 (2012).

- <sup>2</sup>T. Onuma, S. Saito, K. Sasaki, T. Masui, T. Yamaguchi, T. Honda, and M. Higashiwaki, Jpn. J. Appl. Phys., Part 1 54, 112601 (2015).

- <sup>3</sup>T. Oishi, Y. Koga, K. Harada, and M. Kasu, Appl. Phys. Express **8**, 031101 (2015).

- <sup>4</sup>N. Ma, N. Tanen, A. Verma, Z. Guo, T. Luo, H. Xing, and D. Jena, Appl. Phys. Lett. **109**, 212101 (2016).

- <sup>5</sup>Y. Zhang, A. Neal, Z. Xia, C. Joishi, J. M. Johnson, Y. Zheng, S. Bajaj, M. Brenner, D. Dorsey, K. Chabak, and G. Jessen, Appl. Phys. Lett. **112**, 173502 (2018).

- <sup>6</sup>W. S. Hwang, A. Verma, H. Peelaers, V. Protasenko, S. Rouvimov, H. Xing, A. Seabaugh, W. Haensch, C. Van de Walle, and Z. Galazka, Appl. Phys. Lett. **104**, 203111 (2014).

- <sup>7</sup>M. H. Wong, K. Sasaki, A. Kuramata, S. Yamakoshi, and M. Higashiwaki, IEEE Electron Device Lett. **37**, 212 (2016).

- <sup>8</sup>A. J. Green, K. D. Chabak, E. R. Heller, R. C. Fitch, M. Baldini, A. Fiedler, K. Irmscher, G. Wagner, Z. Galazka, S. E. Tetlak, and A. Crespo, IEEE Electron Device Lett. **37**, 902 (2016).

- <sup>9</sup>H. Zhou, M. Si, S. Alghamdi, G. Qiu, L. Yang, and P. D. Ye, IEEE Electron Device Lett. **38**, 103 (2017).

- <sup>10</sup>K. Zeng, J. S. Wallace, C. Heimburger, K. Sasaki, A. Kuramata, T. Masui, J. A. Gardella, and U. Singisetti, IEEE Electron Device Lett. **38**, 513 (2017).

- <sup>11</sup>K. D. Chabak, J. P. McCandless, N. A. Moser, A. J. Green, K. Mahalingam, A. Crespo, N. Hendricks, B. M. Howe, S. E. Tetlak, K. Leedy, and R. C. Fitch, IEEE Electron Device Lett. **39**, 67 (2018).

- <sup>12</sup>Z. Hu, K. Nomoto, W. Li, N. Tanen, K. Sasaki, A. Kuramata, T. Nakamura, D. Jena, and H. G. Xing, IEEE Electron Device Lett. **39**, 869 (2018).

- <sup>13</sup>Z. Hu, K. Nomoto, W. Li, Z. Zhang, N. Tanen, Q. T. Thieu, K. Sasaki, A. Kuramata, T. Nakamura, D. Jena, and H. G. Xing, Appl. Phys. Lett. **113**, 122103 (2018).

- <sup>14</sup>K. Sasaki, M. Higashiwaki, A. Kuramata, T. Masui, and S. Yamakoshi, IEEE Electron Device Lett. 34, 493 (2013).

- <sup>15</sup>M. Higashiwaki, K. Sasaki, K. Goto, K. Nomura, Q. T. Thieu, R. Togashi, H. Murakami, Y. Kumagai, B. Monemar, A. Koukitu, and A. Kuramata, in *Proceedings of the 73rd Annual Device Research Conference (DRC)* (2015), p. 29.

- <sup>16</sup>J. Yang, S. Ahn, F. Ren, S. J. Pearton, S. Jang, J. Kim, and A. Kuramata, Appl. Phys. Lett. **110**, 192101 (2017).

- <sup>17</sup>K. Konishi, K. Goto, H. Murakami, Y. Kumagai, A. Kuramata, S. Yamakoshi, and M. Higashiwaki, Appl. Phys. Lett. **110**, 103506 (2017).

- <sup>18</sup>J. Yang, S. Ahn, F. Ren, S. J. Pearton, S. Jang, and A. Kuramata, IEEE Electron Device Lett. 38, 906 (2017).

- <sup>19</sup>Z. Hu, H. Zhou, K. Dang, Y. Cai, Z. Feng, Y. Gao, Q. Feng, J. Zhang, and Y. Hao, IEEE J. Electron Devices Soc. 6, 815 (2018).

- <sup>20</sup>K. Sasaki, D. Wakimoto, Q. T. Thieu, Y. Koishikawa, A. Kuramata, M. Higashiwaki, and S. Yamakoshi, IEEE Electron Device Lett. **38**, 783 (2017).

- <sup>21</sup>W. Li, K. Nomoto, Z. Hu, N. Tanen, K. Sasaki, A. Kuramata, D. Jena, and H. G. Xing, in *Proceedings of the 76th Annual Device Research Conference (DRC)* (2018), p. 289.

- <sup>22</sup>J. Yang, F. Ren, M. Tadjer, S. J. Pearton, and A. Kuramata, in Proceedings of the 76th Annual Device Research Conference (DRC) (2018), p. 291.

- <sup>23</sup>Å. J. Green, K. D. Chabak, M. Baldini, N. Moser, R. Gilbert, R. C. Fitch, G. Wagner, Z. Galazka, J. Mccandless, A. Crespo, and K. Leedy, IEEE Electron Device Lett. **38**, 790 (2017).

- <sup>24</sup>S. Krishnamoorthy, Z. Xia, C. Joishi, Y. Zhang, J. McGlone, J. Johnson, M. Brenner, A. R. Arehart, J. Hwang, S. Lodha, and S. Rajan, Appl. Phys. Lett. **111**, 023502 (2017).

- <sup>25</sup>Z. Xia, C. Joishi, S. Krishnamoorthy, S. Bajaj, Y. Zhang, M. Brenner, S. Lodha, and S. Rajan, IEEE Electron Device Lett. **39**, 568 (2018).

- <sup>26</sup>M. H. Wong, A. Takeyama, T. Makino, T. Ohshima, K. Sasaki, A. Kuramata, S. Yamakoshi, and M. Higashiwaki, Appl. Phys. Lett. **112**, 023503 (2018).

- <sup>27</sup>A. Kuramata, K. Koshi, S. Watanabe, Y. Yamaoka, T. Masui, and S. Yamakoshi, Jpn. J. Appl. Phys., Part 1 **55**, 1202A2 (2016).

- <sup>28</sup>X. Yan, I. S. Esqueda, J. Ma, J. Tice, and H. Wang, Appl. Phys. Lett. **112**, 032101 (2018).

- <sup>29</sup>M. Mehrotra and B. J. Baliga, in *IEDM Technical Digest* (1993), p. 675.

- <sup>30</sup>G. C. DeSalvo, Int. J. High Speed Electron. Syst. **15**, 997 (2005).

- <sup>31</sup>Y. Zhang, M. Sun, D. Piedra, J. Hu, Z. Liu, Y. Lin, X. Gao, K. Shepard, and T. Palacios, in *IEDM Technical Digest* (2017), p. 9.2.1.

- <sup>32</sup>Z. Hu, K. Nomoto, W. Li, L. J. Zhang, J. H. Shin, N. Tanen, T. Nakamura, D. Jena, and H. G. Xing, in *Proceedings of the 75th Annual Device Research Conference (DRC)* (2017), p. 1.

- <sup>33</sup>L. Zhang, A. Verma, H. G. Xing, and D. Jena, Jpn. J. Appl. Phys., Part 1 56, 030304 (2017).

- <sup>34</sup>B. Song, A. K. Verma, K. Nomoto, M. Zhu, D. Jena, and H. G. Xing, in Proceedings of the 74th Annual Device Research Conference (DRC) (2016), p. 1.

- <sup>35</sup>H. Yano, F. Katafuchi, T. Kimoto, and H. Matsunami, IEEE Trans. Electron Devices 46, 504 (1999).

- <sup>36</sup>T. Kamimura, K. Sasaki, M. H. Wong, D. Krishnamurthy, A. Kuramata, T. Masui, S. Yamakoshi, and M. Higashiwaki, Appl. Phys. Lett. **104**, 192104 (2014).

- <sup>37</sup>T. Kamimura, D. Krishnamurthy, A. Kuramata, S. Yamakoshi, and M. Higashiwaki, Jpn. J. Appl. Phys., Part 1 55, 1202B5 (2016).

- <sup>38</sup>A. Jayawardena, R. P. Ramamurthy, A. C. Ahyi, D. Morisette, and S. Dhar, Appl. Phys. Lett. **112**, 192108 (2018).

- <sup>39</sup>H. Dong, W. Mu, Y. Hu, Q. He, B. Fu, H. Xue, Y. Qin, G. Jian, Y. Zhang, S. Long, and Z. Jia, AIP Adv. 8, 065215 (2018).

- <sup>40</sup>M. A. Bhuiyan, H. Zhou, R. Jiang, E. X. Zhang, D. M. Fleetwood, P. D. Ye, and T. P. Ma, IEEE Electron Device Lett. **39**, 1022 (2018).

- <sup>41</sup>W. Li, K. Nomoto, M. Pilla, M. Pan, X. Gao, D. Jena, and H. G. Xing, IEEE Trans. Electron Devices 64, 1635 (2017).

- <sup>42</sup>H. Zhou, S. Alghmadi, M. Si, G. Qiu, and P. D. Ye, IEEE Electron Device Lett. **37**, 1411 (2016).